Introduction

The NYU Processor Design Team is a Vertically Integrated Project team with the goal of taking novel microprocessor designs from ideation, through RTL design, verification, synthesis, layout, and finally tapeout and validation in real silicon.

Syllabus

Contact Information

| Position | Name | Office Hours | |

|---|---|---|---|

| Course Advisor | Ratan Dey | ratan@nyu.edu | By Appointment |

| Team Lead | Darren Kuo | dk4461@nyu.edu | See Below |

| Onboarding Lead | Noah Mays-Smith | nm4207@nyu.edu | See Below |

Darren’s Office Hours

My office hours are shared with other classes, who will take priority over VIP students. That said, my office hours aren’t busy 90% of the time so don’t hesitate to drop in if you have a question. Email or ping me in the discord to drop into my personal meeting room.

| Day(s) | Hours | Zoom Link |

|---|---|---|

| TBA | TBA | Zoom |

Noah’s Office Hours

My office hours are open for discussion on design strategies or onboarding project related questions. If meeting for questions on the Onboarding Project, both members being present is ideal, but not required. I will also be available for shorter questions during our weekly meetings for shorter questions, and over email if an immediate answer is not needed. For more productive office hours, email me beforehand with your question or problem so I can better help you.

| Day(s) | Hours | Zoom Link |

|---|---|---|

| By Appointment | By Appointment | Through Email |

Course Prerequisites

Students must be pursuing their undergraduate or graduate degree at NYU in order to enroll in a VIP course. Enrollment is based on an application process through the course website. Decisions on acceptance to the course will be made by the faculty advisors. New student decisions are made by the beginning of each semester. Students may apply to various VIP course options (i.e., VIP teams), then select one VIP team to participate on for three consecutive semesters.

For the Processor Design team: Applicants should have completed CS-UY 2214 or ECE-UY 2204 or have equivalent experience with RTL design. Team participation assumes familiarity with Verilog and associated tooling.

About VIP

The Vertically Integrated Projects (VIP) Program operates in a research and development context. Students join VIP teams by enrolling for credit each semester for their participation in design/discovery efforts that assist faculty and graduate students with research and development issues in their areas of expertise. The teams are:

- Multidisciplinary – drawing students from all disciplines on campus

- Vertically-integrated – maintaining a mix of sophomores through PhD students each semester

- Long-term – each undergraduate student may participate in a project for up to three years and each graduate student may participate for the duration of their graduate career

The continuity, disciplinary depth, and professional breadth of these teams intend to:

- Provide the time and context necessary for students to learn and practice many different professional skills, make substantial technical contributions to the project, and experience many different roles on a large, multidisciplinary design/discovery team

- Support long-term interaction between the graduate and undergraduate students on the team. The graduate students mentor the undergraduates as they work on the design/discovery projects embedded in the graduate students’ research

- Enable the completion of large-scale design/discovery projects that are of significant benefit to faculty members’ research programs

Project Objectives

This course operates as an engineering-focused team, research and learning objectives are achieved through building. Team members will be working collaboratively with industry-standard methodology and modern tooling to construct novel microprocessor designs. This VIP course coordinates with the NYU Tandon School of Engineering and the Purdue University SoCET team.

The team has a special focus on modularity of design, toolchain implementation, continuous integration, testing and verification, test coverage reporting, and module packaging. Team members should expect to develop a familiarity with all of these areas prior to developing a specialization.

Learning Objectives

The team seeks to attain the following outcomes for participants:

-

an ability to identify, compartmentalize, and structure solutions to complex problems in digital design using sets of modular components

-

an ability to design and implement repeatable and robust toolchains and workflows using industry-standard tooling

-

an ability to collaborate effectively with team members and integrate diverse, distributed work into a single cohesive solution

-

an ability to independently research and consider possible solutions to a problem space and present concise recommendations for evaluation

Project Structure

This VIP team does not currently have designated sub-teams. A single team-wide meeting will be held weekly at a time determined by participant schedules.

Course Topics

A short list of topics team members will become familiar with:

- System Verilog

- C/C++ for Verification

- Toolchain Automation

- Processor pipelining and pipeline stage implementation

- Caching

- Design flow tooling

- Elements of a PDK

- RISC-V ISA

Course Structure

Time

Students attend weekly meetings and work outside of those meetings individually and/or with team members. The time commitment expected from each undergraduate student is commensurate with the level of variable credit enrollment:

1 credit: 4 hours per week

2 credits1: 8 hours per week

3 credits2: 12 hours per week

Graduate students enroll for 1.5 credits, commensurate with 50 hours over the semester.

Zero-credit enrollment: Students may enroll in VIP for zero (0) credits on a case-by-case basis to address issues of enrollment limitations (e.g., credit limits). This enrollment option can only be used up to 2 times.

Weekly Meetings

Each VIP team determines regular team and/or sub-team meeting times during which students discuss project updates, work on tasks, and plan upcoming objectives. Weekly meetings generally take place for 1 hour.

Students are responsible for participating in their team and sub-team meetings. Contact the VIP Student Leadership and/or VIP Advisor prior to missing a meeting to be excused from attendance. If you miss any meeting, you are responsible for knowing what occurred in that meeting (typically by discussing it with a team member). An excused absence does not relieve you of that responsibility.

Communication

Students are expected to communicate with team members during weekly meetings and through mid-week exchanges. Students are expected to respond to communications in an appropriate time frame and to communicate respectfully. Reach out to VIP team leadership with any issues concerning miscommunication.

The NYU Processor Design team coordinates via Github issues, pull request comments, and our Discord.

VIP Notebook

Every VIP student maintains documentation consisting of meeting notes, details about their work and progress, lists of responsibilities, tasks, and deadlines, reflections, etc.

The notebook format for the Processor Design team is markdown documents submitted as pull requests to this repository. Feedback will be provided in the pull request, and timeliness is judged based on when a PR is submitted.

Team members are expected to update their notebooks weekly. An accepted PR represents full credit for the purposes of grading.

It is not the intent that notebooks represent solely individual work. This is not a test, members’ individual knowledge is not under consideration. Group efforts on labs, developing documentation, or achieving individual or team-wide objectives are all acceptable work for the purposes of the VIP design notebook.

Required Materials

There are no required materials for this course. Introductory project information, training, and resources will be made available to students.

Grades

Students are graded based on participation, contribution, and documentation. Attendance is expected at weekly meetings, and every student reports their individual contributions on a weekly basis through the VIP Notebook.

| Category | Breakdown |

|---|---|

| Documentation (VIP Notebook) | 50% |

| Attendance | 25% |

| End of Semester Presentation or Report | 25% |

| Total | 100% |

Zero-credit enrollment: Students enrolled in a zero-credit VIP course will receive a Pass (P) for 80% or higher.

Documentation

VIP Notebook entries are expected to be updated weekly through PRs by Sunday night. Notebook Entries will be graded out of 2 points:

| Points | Criteria |

|---|---|

| 2 | Entry contains some VIP related Work with basic explanations |

| 1 | Entry does not contain VIP related Work, or is lacking explanation |

| 0 | No Entry Present |

Students are granted up to two unexcused late PRs before penalties on your Documentation grade. For each week a submission is late, there will be a 1 point deduction to that weeks entry.

Attendance

Attendance is expected at all meetings. Meeting time is to be determined based on VIP Members’ availability. If the meeting time does not work for a student, alternate options will be discussed.

Students are allowed 2 unexcused absences. If a student is to miss a meeting they are responsible for anything that occurred in the missed meeting. Students are to notify the VIP Advisor/Leadership team if they are to miss a meeting.

End of Semester Presentation or Report

Typically students will present at the end of the semester on the work that they have completed during the semester. Further details regarding the presentation will be given towards the end of the semester.

Current Membership

Project Leadership:

Project leadership facilitate and administrate the academic aspect of the team, determine high-level objectives, and develop materials for a broad set of team requirements.

Faculty Advisor: Ratan Dey

Team Lead: Darren Kuo

Team Co-lead: Noah Mays-Smith

Czars:

Czars own their respective parts of the technology stack. They have complete discretion to make technical decisions, review change requests, set iteration goals, and develop materials directly related to their objectives.

CPU:

RISC-V core design

Memory:

Memory controller and bus design, and memory compiler integration

AMBA/Peripheral:

Everything AMBA-related, and essential peripherals

Simulator:

Verification simulator development and integration

Software:

RISC-V software and toolchain development

Onboarding/Documentation:

Labs, project documentation, and outreach

Active Members:

Active members are currently enrolled with the team, or were enrolled in the most recent full semester. Each develops their own goals and works in conjunction with project leadership and czars to make sure those goals advance the project and develop valuable technical skills.

VIP

- Joe Aronov

- Mohamed Benaich

- Ghala Buarish

- Yvette Cao

- Tim Chukin

- Calvin Clizer

- Asfaq Fahim

- Srijan Gupta

- Louai Hammad

- Ibrahim Hashim

- Simon Hu

- Vishwas Karale

- Darren Kuo

- Tony Korycki

- Tyler Lee

- Bao Ngyuen

- Danish Puri

- Noah Mays-Smith

- Leo Wang

- Gloria Xin

Design Notebook Guide

Getting Started With Git

Purpose

git is a tool for tracking changes to a set of files, collectively called a

“repository” or “repo” for short. The importance of git is in its distributed

nature. git makes it possible for members of a team to clone a repository,

work on the set of files individually, and then re-integrate those individual

changes into a cohesive whole.

For collaborative projects like the Processor Design Team, these functions

are fundamental to the work we do. Thus, your ability to use git is vital to

participating with the team. With that in mind, you will need to use git

to submit your first (and all future) design notebook entry.

git and GitHub

We need to take a moment to discuss the difference between the tool, git and

the website GitHub. git is a program that runs on your computer and allows

you to track, manage, diverge, and integrate changes to a repository of files.

GitHub is website and web service that understands the protocols and storage

conventions used by the git program.

The advantage of GitHub is it allows users to easily setup and manage remote repositories. A remote repo is a simply a repository that does not exist on your computer, instead the set of tracked files exist on a server, just another computer somewhere on the internet.

Because this repo exists on a continuously hosted internet server, many people can get access to the repo and clone the files. Using Github we can also easily manage who has permission to make changes to the remote repo. If we were hosting our own server we would have to manually create accounts and setup permissions for each person who wanted to access and modify our remote repo.

This is not an idea exclusive to Github. Many different web services are

built around git and allow users to easily create and manage remote repos.

Github is one of the most popular of these services, and it is the one

used by the Processor Design Team which is why it is discussed here.

Github also provides many other services that are unrelated to git the

program. Issue tracking, team management, file browsing, and most notably a

formal pull request mechanism are all features of Github the service, not

git the program.

Creating a Github Account

For the purposes of your design notebook, the first step is going to be creating an account on Github. If you already have a Github account, there is no need to create a new one exclusively for the team.

Configuring git

In any environment where need to use git you first need configure the

program on your current account. You need to tell git your name:

git config --global user.name "Your Name"

And next you need to tell git an email address, this should typically be

whatever email is associated with your GitHub account

git config --global user.email "your_email@example.com"

Setting up SSH Access

ssh stands for “secure shell” and is a encrypted communication

protocol for logging into and communicating with servers. git does not

inherently have a mechanism to communicate with remote repositories, instead it

piggy-backs on existing protocols such as https and ssh. For security

purposes, Github restricts many operations to the ssh protocol.

ssh is built upon the principles of public-key cryptography. What this means

for users is you must generate and store a public/private key pair for use with

the protocol. There is no single way to do this step depending on your

development environment. What follows is a description of how to generate this

key pair and use it with the Anubis ProcDesign IDE environment, but

Github provides excellent instructions

for how to work through this process on a variety of platforms.

The first thing to do is generate a public/private key pair, you can do this with the following command:

ssh-keygen -t ed25519 -C "your.email@nyu.edu"

The generator will ask the following questions:

Enter file in which to save the key (/home/anubis/.ssh/id_ed25519):

Hit enter, as we want to use the default location for this file

The next question will be:

Enter passphrase (empty for no passphrase):

If you enter a passphrase, you will be required to enter it prior to performing most ssh operations. It’s fine to leave this blank.

Now we need to let various operating system components know about your new keys,

so that git will be able to find them later. The way to do this is by using

a command called ssh-add. Unfortunately, ssh-add doesn’t have enough

information to do its job by default. So we need to run a command to retrieve

this information and add it to the local environment. If those words don’t mean

anything to you, don’t worry, just run this command:

eval "$(ssh-agent -s)"

Finally we can add our new ssh keys with the command:

ssh-add ~/.ssh/id_ed25519

The last step is adding your SSH keys to Github, for which you should follow the public Github documentation.

Working With Your Repo

Purpose

While some developers prefer to use git purely from the command line, others

enjoy using the interface built in to their IDE. This is purely a

preference-based decision. In this section, we’ll demonstrate how do work

through some common git operations using both the command line, and how do to

the equivalent operation using the Source Control tab on VSCode and Anubis. Note that most of these features are provided by the GitLens plugin for VSCode and Anubis.

There is far, far more to git than could be productively covered here. It is

highly recommended that you seek guidance from

the Git Book for a complete discussion of both

basic and advanced operations.

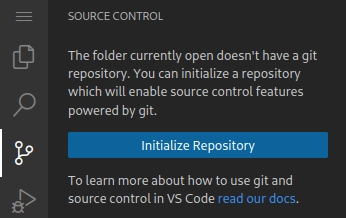

Initializing a Repository

Inside a new empty folder, you can create a new git repo using the command:

git init

This is equivalent to using the “Initialize Repository” button in the Source Control tab:

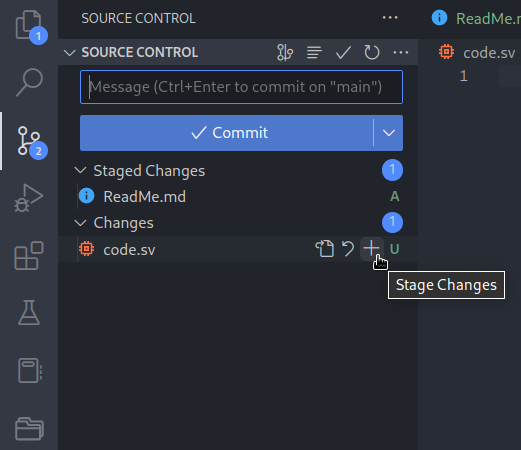

Staging Files

When a new file is added to the project, or changes are made to a file, you can

inform git about those changes with the command:

git add [file_or_folder_names]

This command adds the files to “staging”, which is what we call the set of file changes that we’re going permanently track in the repository.

A common pattern is to use:

git add .

Where the . is a Unix filesystem convention for refering to the current

folder. This command tells git to add all files that have been added or

changed to “staging”.

The equivalent in the Source Control tab is to use the plus and minus signs to move files in and out of “staging”:

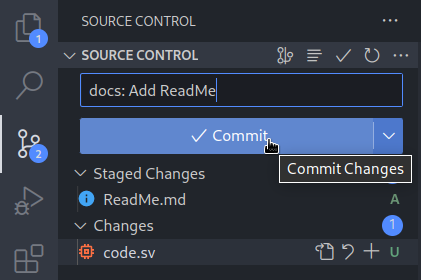

Making a Commit

To make the collection of changes in staging permanent, we make a commit. Every commit is accompanied by a message. You are encouraged, by not required, to follow the conventional commits guidelines for what to write in this message. The czar of a given repo may require this or some other commit message format if you eventually want them to incorporate your changes “upstream”.

The commands to make a commit message depend on how long your message is, commits with short messages can be made with the following:

git commit -m "docs(example): This is a commit message"

If a longer message is needed, the same command without the -m can be used:

git commit

git will open an editor to be filled with the commit message, when the file

is saved and the editor is exited, git will open that file and read the

commit message.

The equivalent in the Source Control tab is the commit box:

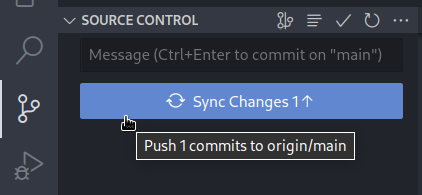

Pushing Changes

Once changes have been made to a local repo, they can be pushed to tracked remotes using the following command:

git push

This is somewhat equivalent to the Source Control operation of “syncing”

Your First Pull Request

Purpose

The pull request is a mechanism for integrating changes between two copies of

the same repository. It is not an inherent process builtin to git, but rather

a formal or informal process built on top of git. In this section we’ll

briefly exam the usage of the GitHub pull request system.

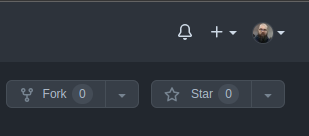

Fork the Repo

A pull request is a request to incorporate changes made on one copy of a repo, into another copy of the same repo. So to start we will need to make a copy to perform changes on. In the case of the design notebooks, the repo to fork is the one that contains the site you’re reading right now.

To understand why you should work on forks, read the next guide - Working Collaboratively.

To create a fork, you need only click the fork button at the top right of the page:

We can now clone the fork as usual.

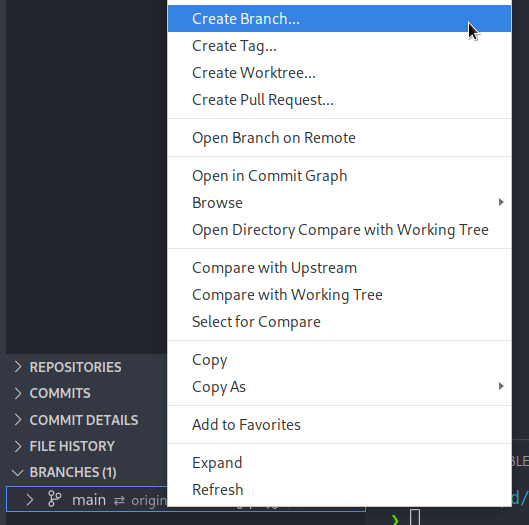

Branching

Before we start making changes, we probably want to branch the repo. This way we don’t mess with the commit history of the “main” branch, so it will be easy to incorporate changes that happen in the main repo we forked from.

To create a branch we can use the following command:

git branch -c branch_name

Then to switch to the branch we can use:

git switch branch_name

These two operations are so common, that there is a shortcut to do them in a single command:

git switch -c branch_name

The same behavior can be found in Source Control by right clicking on a branch you would like to branch from:

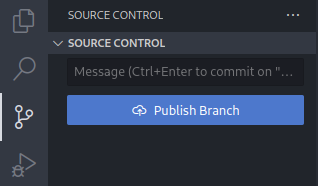

Publishing Changes

After you have added your commits to the branch, you can publish the results to Github with the following commands:

git push [remote_name] [branch_name]

This is equivalent to the Source Control “Publish Branch” button:

Making a Pull Request

To make a pull request, navigate to the “Pull requests” tab of your repo:

And click “New pull request”:

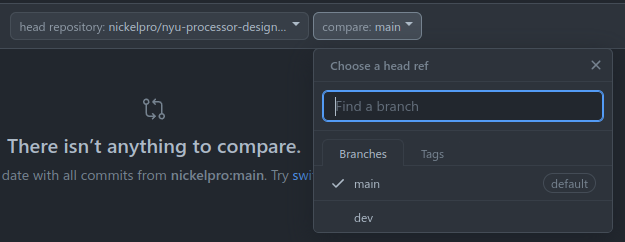

Use the drop-down menu on the right to select the correct branch you would like to pull from:

Now create the pull request.

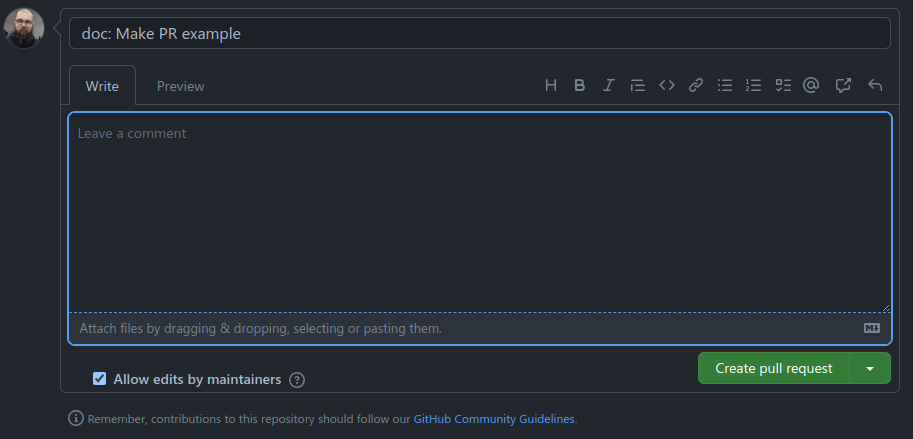

For the following dialogue, it’s fine the leave the title as whatever is generated for the commit. In the comments field, include any information that might be pertinent but isn’t included in the commit itself.

Discarding the Branch

Once your PR has been merged into the “upstream” repository, it is safe to delete the branch you did the work on.

You can do this with:

git switch main

git branch -D branch_name

git push origin -d branch_name

The first command switches off of the development branch, because you cannot delete a branch that is currently checked-out. The second command deletes the local copy of the branch, and the third command deletes the remote copy.

The deletions are equivalent to right clicking and selecting “Delete branch” in Source Control.

Integrating Upstream Changes

You can now pull the upstream changes into your repo, this can be done with

git pull [remote] [branch]

Your First Design Notebook

Purpose

The design notebook is the mechanism used by the team and the VIP program to demonstrate student involvement with the program. As a practical matter, the design notebook serves as an index for an individual’s contributions to the team. Instead of searching through repositories, code, issues, and discussions to find and evaluate what you have done, the design notebook serves as a single point of reference to those materials.

For the Processor Design Team, your design notebook is expected to be principally outbound links to pull requests, repository snapshots, and possibly individual commits, combined with a short (one sentence) contextual explanation of what the linked work is. This is an engineering team and the expectation is that your work is mostly functional, not hypotheticals or explorations of theory. Typical VIP notebook items, such as resources or “task completion” should be implicit in the linked materials.

Format

This website represents the expected format of design notebooks for the Processor Design Team. Every page on this site is built using Markdown files, a plaintext markup language format for quickly producing reasonably formatted HTML documents.

Each VIP student is expected to create a file named netid.md under the

design_notebooks/semester folder of this repository. Where netid is the

student’s NYU NetID (for example, nvg7278.md), and semester is the semester

they are enrolled for (for example, design_notebooks/2023spring).

Each week, students are expected to make a pull request against this repository to update their design notebook file for the semester.

If you are unfamiliar with markdown or wish to revisit its nuances, refer to this markdown cheatsheet.

Content

A typical entry in your design notebook should be a list of items that represent work that was done that week. This list might be longer or shorter depending on the magnitude of each item in the list. If you’ve completed an onboarding lab, a single link to the completed lab repository might be the only item for that week. If you did a little work across project repositories, you might have three or four items linking to PRs, commits, and issue discussions.

Additionally, an entry should have a one or two paragraph personal narrative that contextualizes the work done that week and adds details that can’t be known just from inspection of the linked work. This could be struggles, false starts, or perhaps just the impetus for the work.

Example

## Week of 10 October 2022

Project Work:

* [Onboarding Lab 5](link/to/repo): Completed Lab 5, worked with Jerry and

Rishyak

* [Doc Workflow Update](link/to/pull_request): Updated the documentation

workflow, docs are now generated in ~5 seconds instead of 3-4 minutes

This week was mostly spent on lab 5 from the onboarding series. I worked in

close collaboration with Jerry and Rishyak to complete a suite of system

verilog modules that interoperated to solve the lab objectives.

We struggled with the lab's description "interfaces" and what their

applications were. After a discussion with Prof. Epstein, we gained a better

idea of how to apply interfaces to collect related signals together when

connecting components in a top level module. However, our solution to the

lab doesn't make extensive use of interfaces right now.

Working Collaboratively

Purpose

Collaboration is an essential part of working in any team. Much of our work is shared and built upon each others’ contributions - whether it is the components themselves, editing documentation, or making improvements to this website.

Additionally, as team members join the team with different areas of expertise, it is important to support one another in the learning and development process.

Terminology

upstream: The main repository owned by the organisationorigin: Your fork of the repository

Team Repositories

-

Team members should have access to the NYU Processor Design GitHub organization.

-

Throughout the project, you will need to work on the shared repos - for example, adding a design notebook entry to our website, or editing a component of the AMBA or core.

-

To work efficiently, you want to fork the appropriate repo and make a branch on your fork.

-

After making changes, create a pull request to merge your changes to the team’s repository by following this guide.

-

Once your changes have been merged, delete your branch and update your fork.

Working on Forks

-

When working on your fork of a active and constantly updating repository, you want to avoid working directly on the main branch of your fork.

-

This keeps

mainclean to fast-forward1 any changes from upstream. -

If you work on

main, merging changes from upstream will cause “merge” commits, makingupstreamandoriginhave different histories -

It also creates extra work for the maintainers because they have to clean your fork before merging your changes.

-

Working on

mainwill also create messy pull requests with merge commits and other commits that aren’t associated with your work. -

This ‘pollution’ makes it harder for git to incorporate changes from upstream and may cause merge conflicts, which will have to be fixed

-

Before you start working, make sure to update your fork’s main branch to match the team’s upstream repo.

-

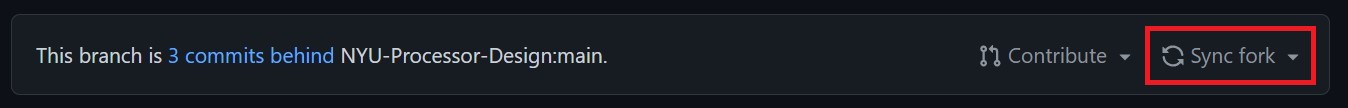

You can use the “Sync fork” button on GitHub

-

Or, locally with the following commands:

git pull upstream main git push origin main

-

-

Then, follow the Your First Pull Request guide.

Fixing Fork Issues

After reading the previous section, you are now realizing your PRs and forked repo are a little messy. Don’t worry, you can clean up your main branch by following the guide below and create a new, beautiful, PR.

Guide

-

Create a branch from your current main branch so you don’t lose any changes.

git branch oldmain -

Clean up your main branch by performing a hard reset from upstream’s main. This will equalise upstream and origin - their histories will be the same. Anything not on upstream will be lost.

git fetch upstream git reset --hard upstream/main -

Force-push your changes to origin

git push -f -

Create a new branch for your changes/work (called

tempbelow):git switch -c temp -

Then, cherry-pick your changes into your temporary branch:

git cherry-pick <commit>...- Where

<commit>...will be the SHA’s of the commits you want to bring over - For example, if you wanted to cherry-pick

1337abc,eb722ec,c00eba4, your command will be:git cherry-pick 1337abc eb722ec c00eba4 - Don’t worry - you’re not expected to know cherry-picking or regularly use it.

- For now, trust that this command will take your changes and store them on your temporary branch.

- If you’re interested, you can find out more about how/why this works in the Pro Git Book.

- Where

-

Optionally, if you have more than one commit, you can squash them into one commit if you know how, but if not, the maintainers can squash and merge your commits into the upstream repo.

- The easiest way to squash commits is to perform an interactive rebase

After cleaning up your fork, you can now create a clean pull request from your branch.

Issues and Questions

-

Nobody’s perfect, which means there may be errors and questions on component modules, git documentation, etc.

-

If you see a problem or have a question, ask the team and/or open a new issue on GitHub using these guidelines.

-

You should also use this contribution guide when submitting a design notebook entry.

Additional Support

-

You are all talented and intelligent – that’s why you’re here – but team members will join the VIP with different levels of experience and knowledge.

-

The best part of working collaboratively is learning from one another and

supporting each other. -

If you see someone struggling or learning something new, offer your assistance in a helpful and respectful way.

-

Fast-forwarding is when git moves the head pointer forward to the tip of the target. You don’t have to actually “merge” the branches. ↩

Developement Environment Guide

- Homebrew Installation (macOS)

- VirtualBox Virtual Machine Guide

- WSL with VSCode Installation (Windows)

- VS Code Extension Recommendations

Homebrew Installation Guide for macOS

Homebrew is a free and open-source software package management system for macOS.

This guide will show you how to install the Homebrew Package Manager on macOS and use it to install the required dependencies for the NYU Processor Design Team.

Contents

System Requirements

- CPU: 64-bit Intel or Apple Silicon

- OS: macOS Big Sur (11) or higher

- Command Line Tools for Xcode

- You can install these by running the following from your terminal:

xcode-select --install

- You can install these by running the following from your terminal:

- Bourne-again shell for installation (You most likely have this)

Installing Homebrew

-

Disclaimer: It is best to not copy-paste commands after the first installation command from this guide. The commands use paths specific to the computer this was written on. That computer also uses Apple Silicon and Homebrew has different installation processes for Intel and Apple Silicon computers. Use this guide as a reference.

-

Open Terminal and run the following command:

/bin/bash -c "$(curl -fsSL https://raw.githubusercontent.com/Homebrew/install/HEAD/install.sh)" -

Next, it will ask you for your password and you should provide the password you use to unlock your computer

==>Checking for `sudo` access (which may request your password)... Password: -

The tool will then display a list of everything it will install and the directories it will create, before asking you to press RETURN/ ENTER to continue, or any other key to abort

-

Press RETURN/ENTER to continue the installation

Press RETURN/ENTER to continue or any other key to abort: -

The tool with then start to install Homebrew and any needed Xcode dependencies

- Let the command run fully and do not close the terminal

- It may appear at times to be stuck or frozen but it is simply downloading the files it needs

- Many of these files such as the Xcode command line tools are rather large so expect the installation to take several minutes.

-

You will know the installation is done when the following shows up on the Terminal:

==> Installation successful! ==> Homebrew has enabled anonymous aggregate formulae and cask analytics. Read the analytics documentation (and how to opt-out) here: https://docs.brew.sh/Analytics No analytics data has been sent yet (nor will any be during this install run). ==> Homebrew is run entirely by unpaid volunteers. Please consider donating: https://github.com/Homebrew/brew#donations ==> Next steps: -Run these three commands in your terminal to add Homebrew to your PATH: echo '# Set PATH, MANPATH, etc., for Homebrew.' .. /Users/test/.zprofile echo 'eval "$(/opt/homebrew/bin/brew shellenv)"' >> /Users/test/.zprofile eval "$(/opt/homebrew/bin/brew/ shellenv)" - Run brew help to get started - Further documentation: https://docs.brew.sh -

You will then need to run the following three commands one at a time to fully set up Homebrew

- These commands will allow you to access the homebrew commands from your terminal

- Remember to change the username from the path from

testto whatever your username is if you are copying commands from this guide

-

Adds a comment in your

zshprofile fileecho '# Set PATH, MANPATH, etc., for Homebrew.' .. /Users/test/.zprofile -

Adds homebrew to your

PATHecho 'eval "$(/opt/homebrew/bin/brew shellenv)"' >> /Users/test/.zprofileeval "$(/opt/homebrew/bin/brew/ shellenv)" -

Run the following command to confirm your installation

brew help

Installing Packages

-

The installation command for Homebrew is:

brew install <package name>- This will search for the specified package1 in the brew registry and install it in your system.

- You can list multiple package names in one command, for example:

brew install cmake verilator clang-format

-

Homebrew installs packages in

/usr/local/Cellar/by default -

It will then make symlinks to the package at

/usr/local/opt/and/usr/local/bin/so the packages can be used as executables -

If you want to get information about a specific installed package, you can use the

brew infocommand like this:brew info <package name> -

macOS comes with most dependencies pre-installed, so you only need CMake and Verilator

- To install said dependencies, run the following commands in the Terminal

CMake

brew install cmake

Verilator

brew install verilator

Maintaining Packages

-

To update Homebrew and package definitions, regularly run the following

brew update -

Upgrade everything

brew upgrade -

Upgrade a specific package

brew upgrade <package name> -

Uninstall a package

brew uninstall <package name>

Further Reading

- If you want to explore more about Homebrew or run into any trouble visit the official site or the FAQs for many more guides and explanations.

-

Homebrew calls these “taps” or “bottles”, depending on how they are installed ↩

VirtualBox Guide

Last updated February 7, 2024

VirtualBox (VBox) is a popular hypervisor1 for x86 virtualisation. It allows you to create virtual machines, which are effectively emulations of computers on your computer. This allows you to use operating systems you do not have on disk, run programs that may be risky to run on your computer, or work with historical machines that are hard to find now.

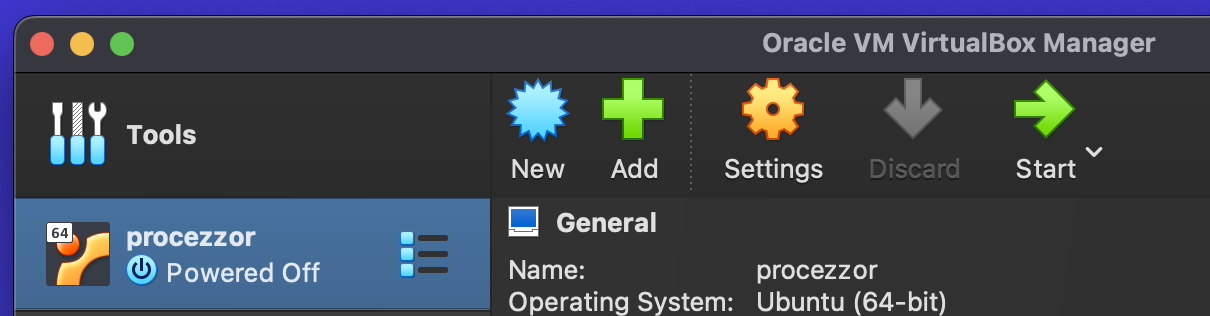

We will use VirtualBox to create a virtual machine (VM) to contribute to the NYU Processor Design Team without having to install Linux natively or buy a new computer. VBox is a plug-and-play solution for all intents and purposes of the NYU Processor Design Team.

This guide will help you use the provided VM configuration with VBox.

Contents

- Minimum Requirements

- Virtual Machine Information

- Downloading VirtualBox

- Downloading the VM

- Importing the VM

- Starting the VM

- Logging In

- Homescreen

- Exploring your VM and Tips

- Configuring your VM

Minimum Requirements

-

CPU: Any reasonably powerful 64-bit x86 processor

(fancy for “most modern computers”) -

Memory: 8 GB RAM

-

Disk Space: 16 GB available space

(Virtual hard disks are dynamic and grow with usage. You do not need 16 GB available immediately, that’s just what the VM is set up for) -

OS: Any major 64-bit operating system such as Windows, macOS, and most Linux distributions

Note: If you already use Linux or macOS, you can start working immediately and do not need a VM, but nobody will stop you if you wish to use one regardless. Check the Lab Guidance page for what you need to have. Optionally, macOS users are encouraged to look at the Homebrew Installation Guide.

Virtual Machine Information

-

The provided VM is set up for VirtualBox >7.0.0, which means it is guaranteed to work with any version of VBox after 7.0.0

-

Currently, VirtualBox is on 7.0.14, as of writing this guide

-

The VM is set up with Ubuntu Desktop 23.10 Mantic Minotaur

-

The VM contains all tools you need to begin working right away

Specifications

-

OS: Ubuntu Desktop 23.10

-

Processors: 4 processors

-

Memory: 6 GB RAM

-

Disk Space: 16 GB

-

Appliance Size2: 8 GB

Note: You can edit these later to your desire if your computer has more resources to allocate to the VM.

Downloading VirtualBox

-

Go to virtualbox.org

-

Download the latest version of VirtualBox

Downloading the VM

-

Go here

-

Download the

.ovafile- OVA stands for Open Virtualisation Appliance

- It is a common file extension that hypervisors use

- The NYU Processor Design Team VM contains the entire OS, some applications, utilities, etc. and therefore, is ~7 GB.

Importing the VM

-

Open VBox

-

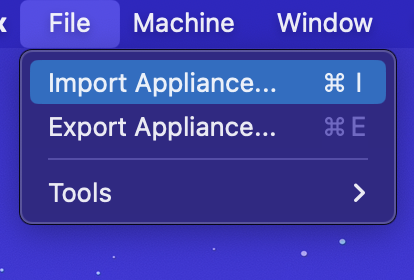

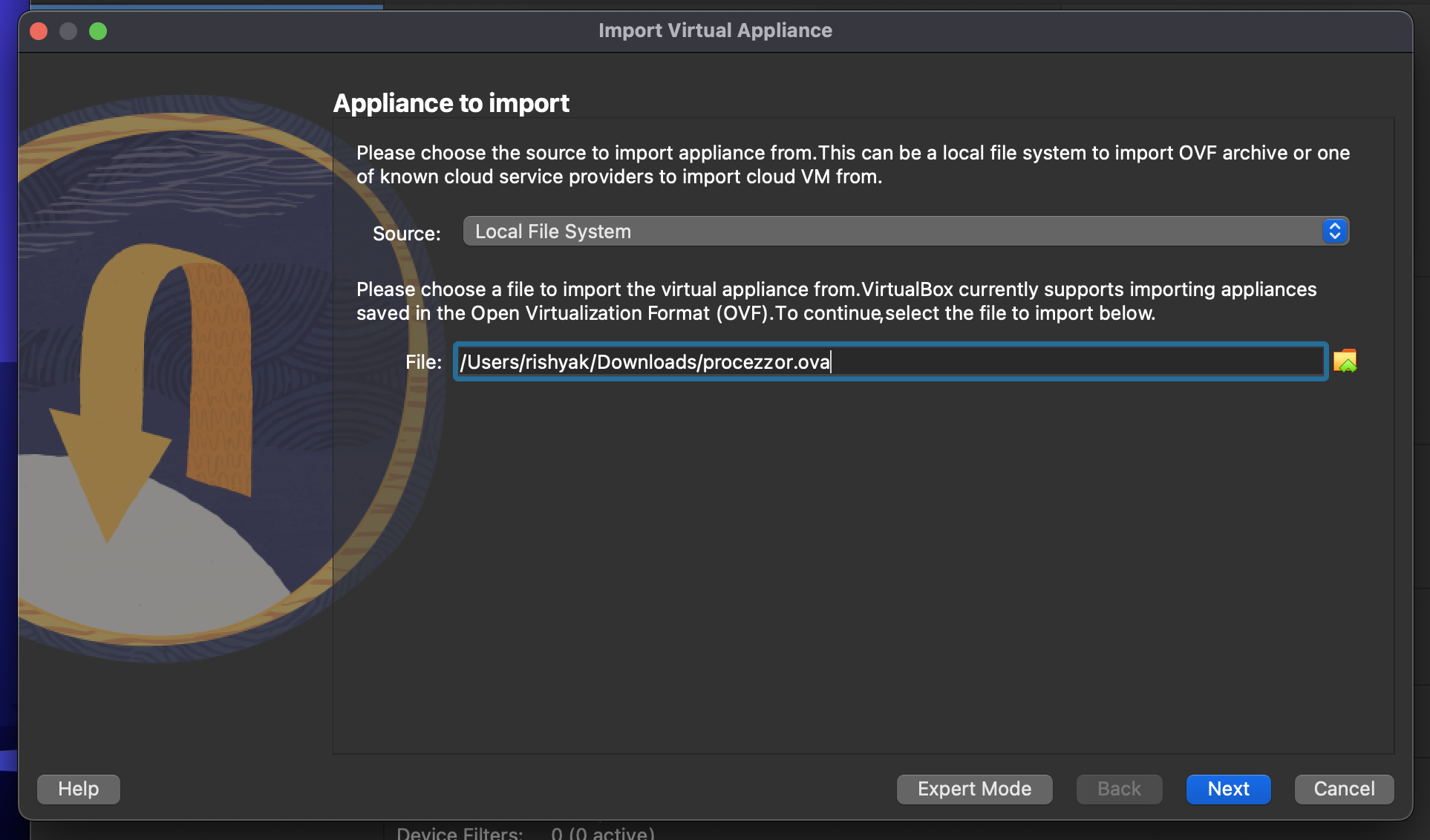

Click on “File” and then “Import Appliance”

-

Find the

procezzor.ovafile in your file system

-

Click

-

Keep all the default options, click

Starting the VM

- Double-click on the VM or press

Logging In

-

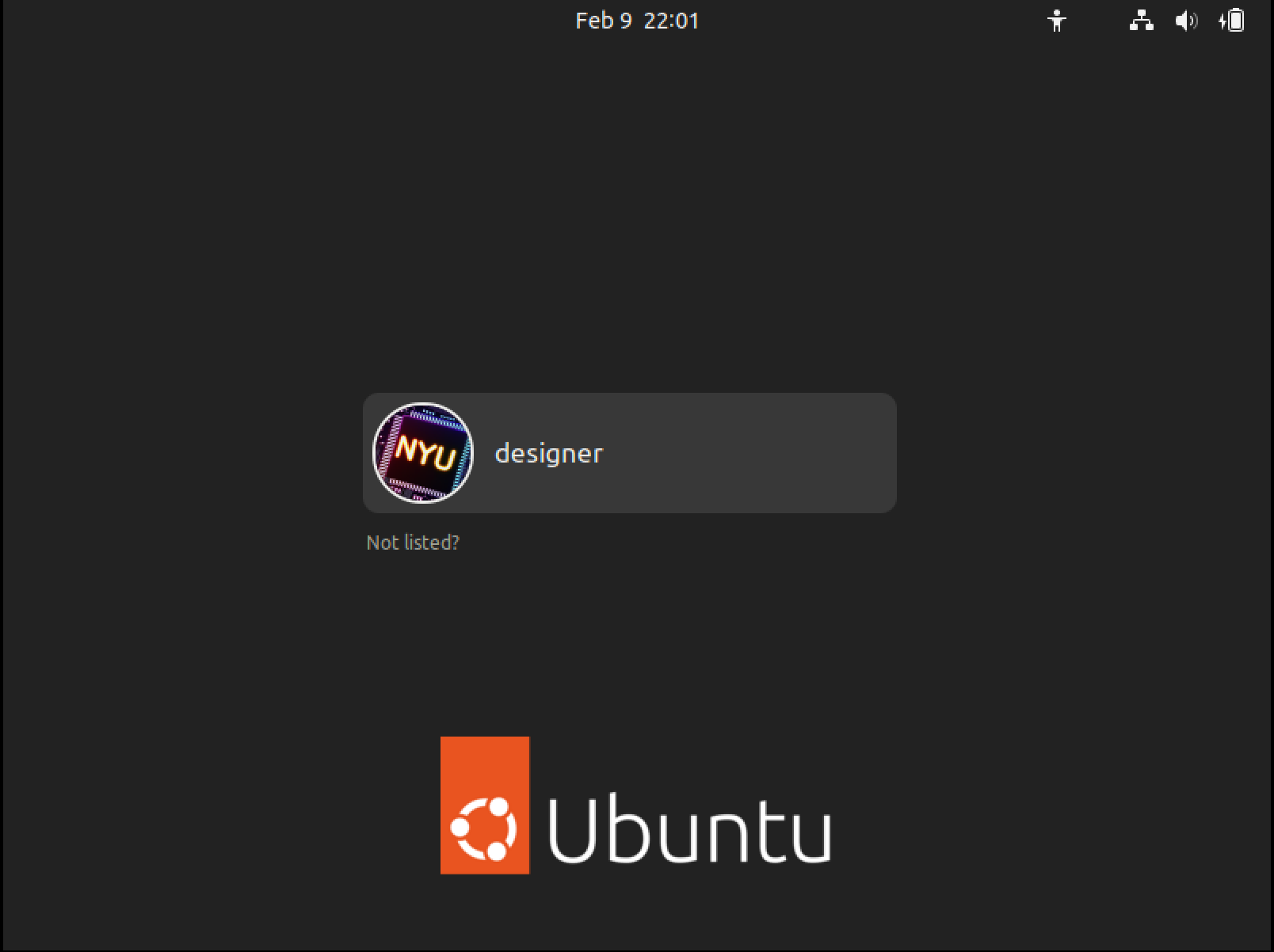

You will now be presented with a log-in screen like this:

-

Click on the “designer” user and you will see this:

-

Enter the password “processor” and hit Enter/Return

-

You will now be presented with the Ubuntu homescreen (the wallpaper might be different)

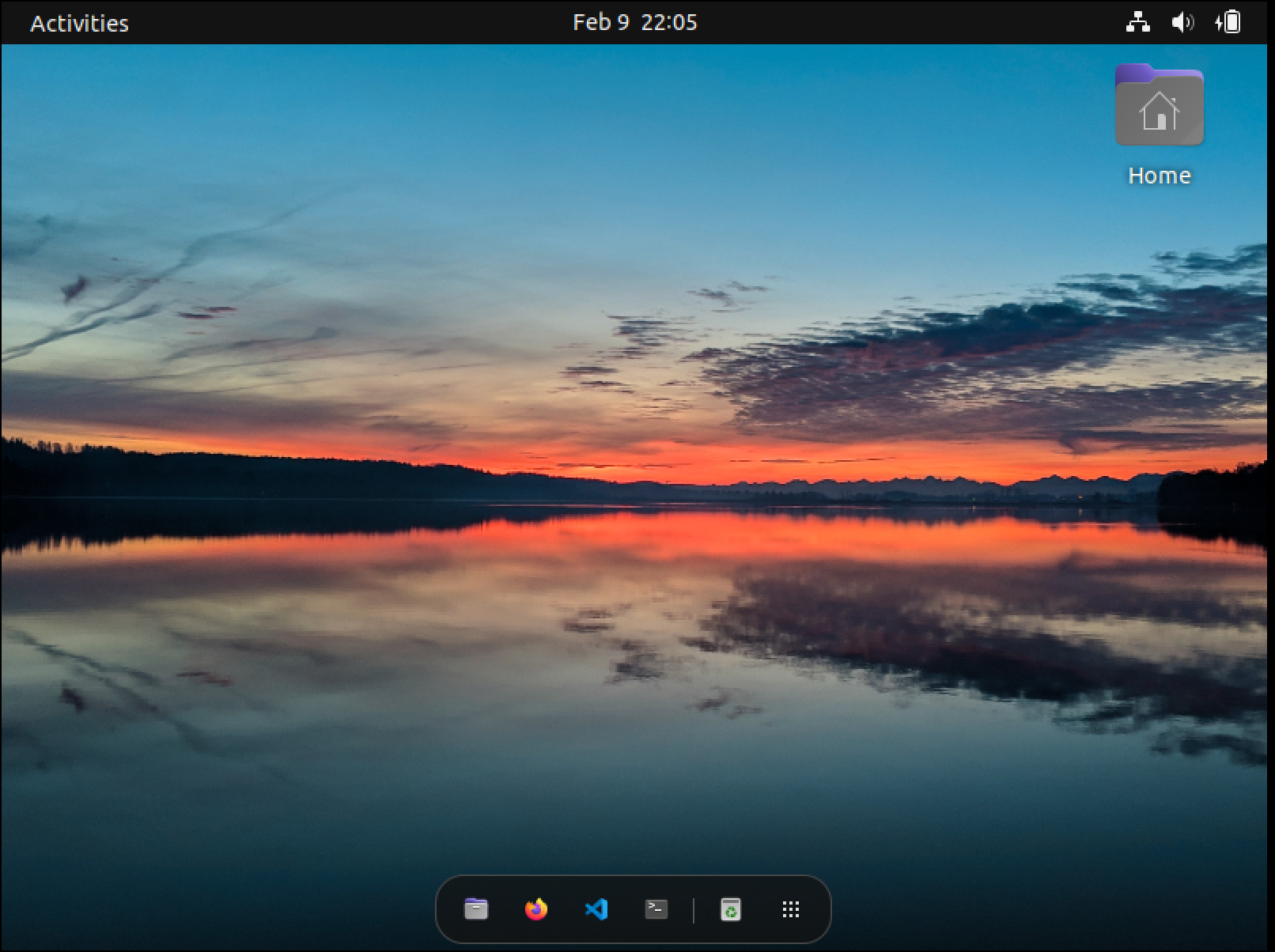

Homescreen

-

You will see the home folder on the Desktop, in the top-right corner

-

On the dock, you will see:

- Files (the file explorer)

- Firefox (browser)

- VS Code (text editor) with some useful extensions:

- C/C++

- CMake and CMake Tools

- GitLens

- System Verilog Language Server

- Terminal

- Recycle Bin

Exploring your VM and Tips

-

Now you have a Linux VM to play around with

-

You can do whatever you want with it

- Since this is not a real computer, you do not have to worry about breaking it so play around

- Worst case: Just re-install the VM

- Word of advice: It’s best to stay away from playing with root, bad things can happen

-

Although, it is recommended that you change the password

- You can do so through settings or by opening the terminal and typing:

passwd -

You can also go through the settings and customise it to your preferences - remember, it is now your virtual computer

-

You should regularly run the following two commands:

-

Update and upgrade packages

sudo apt update && sudo apt upgrade -yupdatefetches the latest information of the installed packagesupgradewill upgrade them if newer versions have been released- the

-yflag simply tells APT that it has permission to upgrade everything and doesn’t have to ask you to say “yes” to each upgrade

-

Update Snap packages

sudo snap refresh -

Snap is Canonical’s3 deployment system

- Ubuntu’s equivalent of the App Store/Play Store/Windows Store

-

-

You can close your VM by clicking on the close button, choosing whether to keep the machine frozen in its current state or shut down completely; you can also use the power options in Ubuntu

Configuring your VM

-

This VM was created for the average computer one may have

-

If you have a more powerful computer, you would benefit from increasing the resources your computer can dedicate to the VM

-

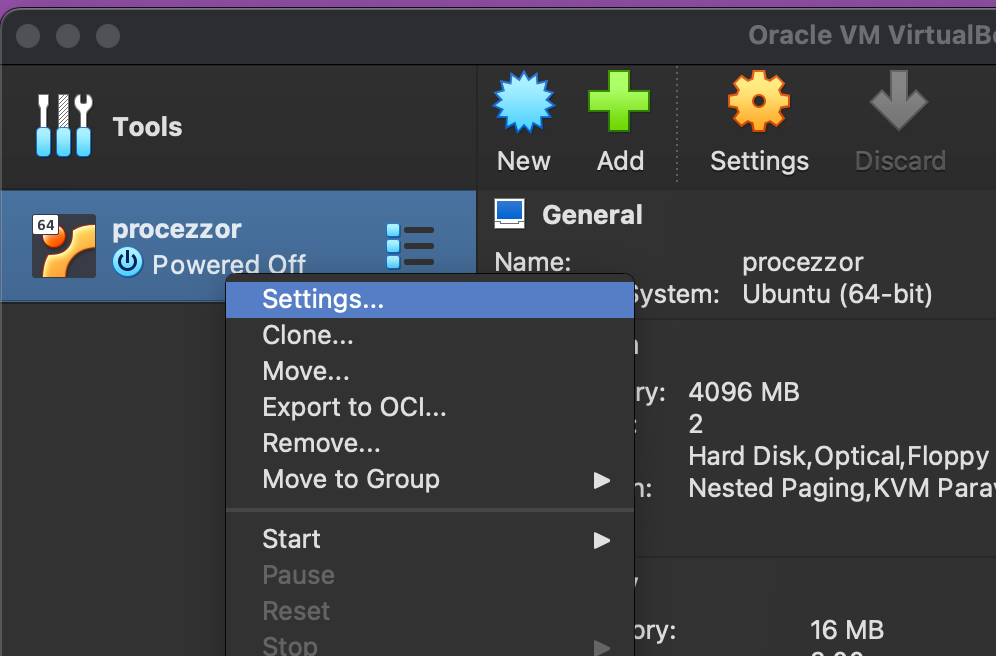

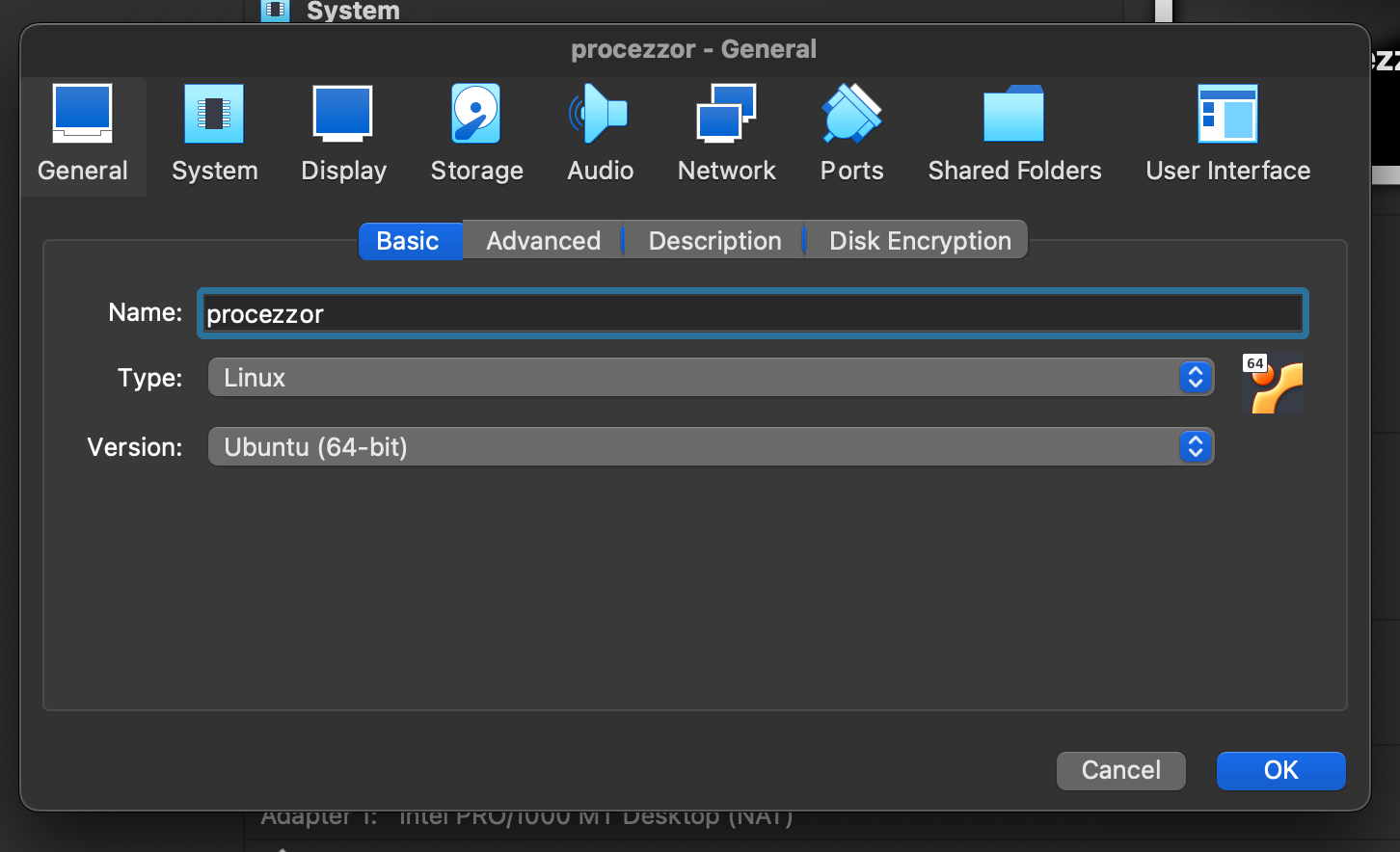

To do so, press Control/Command+S or right-click and then choose “Settings” or click on the bright-orange cog symbol in the ribbon

-

You will see the settings screen

-

Here, you can click through the various sections and configure your VM

- Word of Advice: It is best to not mess with most of these

-

You should look at the “System” and “Display” tabs and adjust the settings for your computer

- It is recommended to give a quarter to a half of all your resources to a VM

-

Play around with these settings and your VM will feel like a native install in no time

-

A hypervisor is software that runs and monitors virtual machines ↩

-

The file contains everything you need to begin working, hence the size ↩

-

The company that develops and maintains Ubuntu ↩

Windows Subsystem for Linux (WSL) Installation Guide

The Windows Subsystem for Linux (WSL) is a type 1 hypervisor1 developed by Microsoft to allow developers to run Linux environments directly on Windows, without the drawbacks of type 2 hypervisors1 such as virtual machines, or, the hassles of dual-boot setups.

This guide will show you how to install the Windows Subsystem for Linux (WSL) on Windows and use it to install the required dependencies for the NYU Processor Design Team.

Contents

- Installing WSL

- Using VSCode with WSL

- Installing Packages (Ubuntu)

- Maintaining Packages

- Optional: Using Zsh

- Further Reading

Installing WSL

-

Open a Terminal and run the following command:

wsl --install -

The following command will install the default Linux distribution (Ubuntu), but you can install any of the distributions listed by

wsl -l -owsl --install -d <distribution_name> -

After a restart, running the command

wslin the terminal or running thewslcommand in your start menu will open a virtual linux environment in your pc -

Once WSL has been set up you will have to create a username and password for your linux machine

-

Follow the instructions provided and remember the password you enter as it will be required to run

sudocommandssudostands for “Super User Do”

Using VSCode with WSL

-

Install VSCode in your native Windows environment first.

-

In VSCode, install the WSL extension using the Extensions tab on the left tool panel

-

Now, VSCode can be run in the WSL environment by doing one of the following:

- Clicking on the “Remote Window” button at the bottom left of your

VSCode window and clicking “New WSL Window”

- Pressing F1 or Control+Shift+P

to open the command palette and selecting

WSL: New WSL Window

- Clicking on the “Remote Window” button at the bottom left of your

VSCode window and clicking “New WSL Window”

Upgrading the Ubuntu Version

By default, WSL only has LTS (Long-term support) versions available. This doesn’t work for us because we want to use more up to date packages that are only available in more recent versions.

- If the second sed command fails, you might want to open

sources.listand see a line like thisdeb http://archive.ubuntu.com/ubuntu/ jammy main restricted. If instead of jammy, it saysfocalor

Before you begin, open sources.list, and find a line like deb http://archive.ubuntu.com/ubuntu/ jammy main restricted. If instead of jammy,

you see focal or bionic, switch jammy to focal or bionic in the commands

below.

cat /etc/apt/sources.list

- The first step is to switch from the LTS branch to the normal Ubuntu branch

sudo sed 's/lts/normal/g' /etc/update-manager/release-upgrades - Next, the package sources need to be pointed to lunar instead of jammy.

sudo sed -i 's/jammy/lunar/g' /etc/apt/sources.list - Once the sources are updated, the existing packages must be upgraded to the new version. This can take several minutes to complete.

sudo apt update sudo apt upgrade sudo apt dist-upgrade

Troubleshooting

Installing Packages (Ubuntu)

- The installation command for Ubuntu is

sudo apt install <package name>- This will search for the specified package in the APT registry and install it in your system.

- You can list multiple package names in one command, for example:

sudo apt install verilator clang-format

CMake

Unfortunately, APT doesn’t have the latest version of CMake, so we must use this alternative2.

-

Uninstall existing CMake Versions

sudo apt remove --purge --auto-remove cmake -

Preparing for Installation

sudo apt update && \ sudo apt install -y software-properties-common lsb-release && \ sudo apt clean all -

Obtain a copy of kitware’s signing key

wget -O - https://apt.kitware.com/keys/kitware-archive-latest.asc 2>/dev/null | gpg --dearmor - | sudo tee /etc/apt/trusted.gpg.d/kitware.gpg >/dev/null -

Add kitware’s reposity to sources list

sudo apt-add-repository "deb https://apt.kitware.com/ubuntu/ $(lsb_release -cs) main" -

Optionally, installing kitware-archive keyring package to keep Kitware’s keyring up to date

sudo apt update sudo apt install kitware-archive-keyring sudo rm /etc/apt/trusted.gpg.d/kitware.gpg -

If running

sudo apt updategets the following error:

Copy the public keyErr:7 https://apt.kitware.com/ubuntu bionic InRelease The following signatures couldn't be verified because the public key is not available: NO_PUBKEY 6AF7F09730B3F0A4 Fetched 11.0 kB in 1s (7552 B/s)6AF7F09730B3F0A4and run this command:sudo apt-key adv --keyserver keyserver.ubuntu.com --recv-keys 6AF7F09730B3F0A4 -

Finally, update and install the

cmakepackagesudo apt update sudo apt install cmake

Verilator

sudo apt install verilator

cURL

sudo apt install curl

Git

sudo apt install git

- Then follow the Getting Started With Git tutorial to configure git

Maintaining Packages

-

To update APT and package definitions, run the following

sudo apt updateupdatefetches the latest information of the installed packages

-

Upgrade everything

sudo apt upgrade -yupgradewill upgrade them if newer versions have been released- the

-yflag simply tells APT that it has permission to upgrade everything and doesn’t have to ask you to say “yes” to each upgrade

-

Uninstall a packages

sudo apt remove <package name>

Optional: Using Zsh

-

Ubuntu’s default shell is the Bourne-again shell (Bash)

-

Z-shell (Zsh) is a Unix shell built on top of BASH

-

Zsh includes more features and is the default shell on other popular Linux distros such as Arch Linux

-

To replace Bash as Ubuntu’s default shell, first install zsh:

sudo apt install zsh -

Change login shell to Zsh

chsh -s $(which zsh)chshchanges your login shell- The

-sflag specifies the login shell - The

$()syntax tells the shell to interpret everything between the parentheses as a command whichidentifies the location for various executables and prints the full path of the executables; in this case, we want the path forzsh

-

Log out and log back in for the change to take effect

Prettifying Zsh

-

The default Zsh appearance is, for the lack of better words, hideous, unpleasant, and unsightly

-

To fix this, many open-source frameworks have been created to create themes for Zsh terminals

-

Oh My Zsh is the most popular Zsh theme framework

- Sidetrack: Fun story about the ideation of Oh my Zsh, written by the creator, Robby Russel

-

Not only does it make Zsh much more pleasant to look at, it also provides useful and important information such as your current working directory, git branch, git status, etc.

-

To install Oh My Zsh, use the following command

sh -c "$(curl -fsSL https://raw.githubusercontent.com/ohmyzsh/ohmyzsh/master/tools/install.sh)" -

To change the theme of your terminal, you can run the command

nano ~/.zshrcand change the lineZHS_THEME="robbyrussell"to any of the available themes listed here- The

.zshrcfile is a special run-command file that contains configurations for your zsh terminal session - It exists on your home directory as a hidden file, hence the

~and.beginning - It is executed when you log in

- The

Changing VSCode’s Default Terminal

-

To change VSCode’s default terminal, press F1 or Control+ Shift+P to open up the command palette

-

Search for

Terminal: Select Default Shelland selectzsh -

Now every time you open a terminal in WSL, VSCode will open a zsh terminal

Further Reading

-

Microsoft’s excellent documentation for WSL

-

VSCode’s excellent documentation on developing in WSL

-

Ubuntu’s documentation about Ubuntu on WSL

-

TroubleChute’s documentation on how to update Ubuntu from one release to another.

-

A hypervisor is software that runs and monitors virtual machines ↩ ↩2

-

Summarized from this Stack Exchange question ↩

Useful Extensions for VSCode

VSCode has many extensions and tools that may be helpful in the development process for the NYU Processor Design team. This guide is a compilation of recommended VSCode extensions. Most installation instructions can be found in the associated links.

Contents

- SystemVerilog Language Server

- C++ Pack

- Doxygen Generator

- Better Comments

- Spell Checker

- Git & GitHub

- Markdown All in One

- Optional Bonuses

SystemVerilog Language Server

SVLangserver is a language server for System Verilog that features auto-completion, module hierarchy, code snippets for common blocks, code formatting, syntax highlighting, and more.

To install, find svlangserver in the VSCode marketplace. You can modify your extension settings to your desired preferences as detailed in the link above. The extension’s commands and troubleshooting can also be found in the link.

C++ Pack

This extension pack has 4 sets of popular extensions:

- C/C++ support

- C/C++ Themes

- This is simply a visuals/aesthetic extension; not necessary, just part of the extension pack. You can use whatever theme you like.

- CMake support

- CMake Tools

Doxygen Generator

Doxygen is a documentation generator that extracts documentation from C++ source code comments. This Doxygen comment generator creates Doxygen comments for a variety of code snippets: constructors, functions, file descriptions, etc.

Better Comments

Better Comments helps to create more understandable, categorizable comments for your code, and works with C++ and Verilog.

Spell Checker

This Code Spell Checker does exactly that: it is a basic spell check that can be customized and has a variety of add-on language dictionaries.

Git & GitHub

GitLens

GitLens is a customizable extension that includes a wide variety of features such as a Git command palette, and detailed commit, repo, and branch histories. Full details can be found in the link above.

Note: This is a highly recommended extension, and the Pro version is free with GitHub’s Student Developer Pack.

GitHub Actions

GitHub Actions lets users manage workflows and view workflow history for github.com hosted repositories.

GitHub Pull Requests

The GitHub Pull Requests and Issues extensions lets you review and manage GitHub PRs and issues directly in VSCode.

Markdown All in One

Markdown All in One is a collection of Markdown commands and features like keyboard shortcuts, math, table of contents, etc.

Optional Bonuses

ColdCode

ColdCode is used to take screenshots of your code with various configuration options (show line numbers, titles, etc).

Makefile Tools

Makefile Tools provides IntelliSense configurations to the C/C++ Extension for Makefile projects. It also has commands to build, debug, and run targets.

GitHub Style Markdown Preview

This extension lets you preview Markdown files using GitHub’s styling, and is customizable with GitHub’s various themes.

Marp

Marp is used to create slide decks in Marp Markdown directly in VSCode. (For our Google Slides haters and VSCode lovers, we got you.)

Rewrap

Rewrap performs hard wrapping for comment blocks and any kind of plain text files.

Onboarding Labs

Lab Guidance

Purpose

What follows is generic guidance applicable to all of the Onboarding Labs

Guidance

-

Labs do not require any specific computing environment so long as the required tools are present. You are free (and somewhat encouraged) to work on a personal machine. However, all of the requirements for the labs are provided on Anubis if you don’t have a development machine that can run the required tooling.

-

For a personal computing environment, the required tools across all the labs are the following:

-

cmake

-

verilator

-

git

-

curl

-

zip, unzip

-

tar

-

-

Labs are intended to be run and completed in their own directory/repository. If a lab requires you to clone an existing repository and work inside it, that will be noted in the instructions.

-

For the purposes of the design notebook, you will need to push the final state of a given lab directory to a repo. You can then link to this repo in your design notebook, see the Design Notebook Guide for more.

-

Labs may ask that you Make Note or Answer the following at various points in their instructions. These notes and answers should be collected in a

ReadMe.mdfile in the root of the lab directory. There is no specific layout required for this file, other than it should be obvious what notes and questions correspond to which answers.

Lab 1: CMake and Toolchain

Before You Begin

Take some time to review the Lab Guidance before beginning on these labs. If you’re using the labs to populate your design notebook entries, failure to follow the lab guidance could adversely affect your Documentation grade.

Purpose

In both hardware and software development, we use a variety of tools to achieve our goals, tools such as compilers, linkers, simulators, etc. These tools can be quite complex, have non-trivial inter-dependencies, and the overall process of invoking all the necessary tools to build the final product may have many steps.

For projects of sufficient complexity, it is rarely feasible and never desirable

to run all the necessary tools by hand. Instead, we write programs to run the

tools for us. These programs are collectively referred to as the

toolchain. In this lab, you will learn to work with the major toolchain

program used by the Processor Design Team, a tool called cmake.1

Part 1: CMake Hello World

cmake is a tool for describing toolchains. Typical usage of cmake looks

like:

cmake [directory]

Where [directory] is a location on the filesystem that contains a file named

CMakeLists.txt. This file is often referred to as an acronym, “CML”, and we will do so in these lab instructions as well.

We will start by creating an empty CMakeLists.txt file in the lab directory.

Before we put any commands into the file, we need to know what version of

cmake we are running. We can discover this with the command:

cmake --version

Make Note: What version of cmake is running in your environment?

The cmake version number is split into three parts, separated by periods. The

first is called the major version, the second the minor version, and the

third is called the patch number. These make up a system known as

semantic versioning which we will discuss more in a later

lab.

Now we are ready to add the first line of code to our CML file, and it should look like this:

cmake_minimum_required(VERSION [major].[minor])

In this line of code, [major] and [minor] should be the major and minor

version number you learned from the earlier command. As you might suspect,

cmake_minimum_required is a cmake command which will ensure the cmake tool

running the file is at least of a minimum version. Unless you’re specifically

testing or making certain your CML runs on older cmake versions, it’s best to

set this to the version of cmake you’re currently using.

The next line of code isn’t strictly necessary for "Hello World", but you will

see it in nearly every CML so we’ll include it here too:

project(week-one-lab VERSION 1.0.0)

Here we have the project name and version number for our code. This isn’t very significant yet, but it will be in the future.

It’s time to make the magic happen, the third line of your CML will be:

message("Hello World")

Now we’re ready to run cmake. First, create a directory named build inside

your lab folder. In a console, navigate to the build directory and run the

command cmake ... The .. tells cmake to look for our CML file in the

parent folder of our current working directory.

cmake will generate an amount of output, but among its many messages should be

our "Hello World"!

Part 2: Building a Program

The astute student will notice that our build directory is now filled with

random crap. This is, in fact, why we created the build directory. In the

future, we’re always going to want to run cmake in its own directory for

this reason, so that the generated files don’t pollute our source code folder.

But what are all these files? What purpose do they serve? Before we answer

that question, let’s try to build an actual program with cmake. First,

write a Hello World program in C++ and save it as hello.cpp at the top

level of the lab repository (the same folder which holds the CML).

Next, we’re going to tell cmake we would like to build a program, using the

following two lines of code. You can remove your message() command from the

CML and replace it with:

add_executable(hello_world)

target_sources(hello_world PRIVATE hello.cpp)

The first line informs cmake about the new program named hello_world that

we would like to create, and the second tells cmake about a source code file

we would like to associate with this new program, and that’s it! (We’re going

to ignore that PRIVATE keyword for now).

Inside the build directory, run the cmake .. command again to re-run the

cmake tool on the edited CML.

Unfortunately, our program has not been created. In fact, the files inside the build directory are exactly the same files as before. Before we answer that question, let’s get a working hello world program. The following command, run inside the build directory, will build the final program:

make

The command is make not cmake

Make Note: Run make help and figure out what the valid targets (command

arguments) are for this project. For all the targets that start with “hello”,

can you figure out what they produce? What about all and clean?

Despite their similar names, make and cmake are completely unrelated

programs. make is a build system, it produces a final program executable that

you can run. cmake is a meta-build system, it reads the CML and produces

other build systems, such as the Makefile that make uses to build our

hello_world program.

Just like a compiler can support multiple computer architectures, cmake

supports multiple build systems. In the build directory, try running the

following commands so that cmake will generate a ninja build system instead

of a make build system (the first command removes the old files from the

build directory, to prevent errors):

rm -rf *

cmake -G Ninja ..

Now you can run the ninja command in the build directory to produce the final

binary. Optionally, you can run cmake --build . and cmake will run the

correct build tool for whichever build system was generated.

Why is this so complicated? Historically, build systems were either fast and

hard to use or very slow but flexible and easy to use. cmake’s solution to

this problem was a flexible tool that generates a fast build system. The ninja

build system in particular is never meant to be used directly by humans, but

only as a target for other programs like cmake.

Part 3: Adding More Files

Now that we have basic cmake usage down, there’s only a little more left to

talk about before you’re ready to strike out on your own.

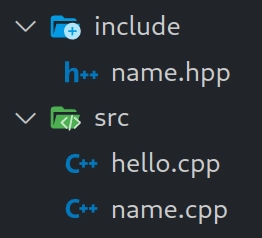

Let’s create a more typical file structure, we’re going to have an src

directory that holds C++ implementation files, and an include directory

that holds C++ header files. We’re also going to create two new files,

name.cpp and name.hpp. The final file structure should look like this:

In name.cpp write a function that asks the user their name, and returns it as

a std::string and add the function declaration to name.hpp. In hello.cpp,

include the header file with #include "name.hpp" and call the associated

function so that you can greet the user by name.

We can modify our target_sources command in the CML to account for the new

file locations:

target_sources(hello_world PRIVATE src/hello.cpp src/name.cpp)

It would also be acceptable to do this across multiple commands:

target_sources(hello_world PRIVATE src/hello.cpp)

target_sources(hello_world PRIVATE src/name.cpp)

Header files do not need to be added directly, instead, we just need to inform the build system what directories to search for them in:

target_include_directories(hello_world PRIVATE include)

You should now be able to build and run your modified hello world program

Answer the following:

-

The paths used by

target_sourcesandtarget_include_directoriesare relative, not absolute. What file or folder are they relative to? -

What are some differences between

cmakeandninja? -

Why is it important to run

cmakein its own directory?

-

You may wonder, “Why do I have to learn this before I’ve written any code?” In programming classes where you only had to run a compiler on a single file, it was fine to just invoke the compiler directly. For hardware design, even the simplest designs will involve running dozens of commands. It would slow you down significantly if you didn’t know how to use the toolchain before moving into the actual design process. ↩

Lab 2: System Verilog

Purpose

This is a crash course in basic System Verilog constructs. As some level of exposure to Verilog is a requirement for access to the team, this lab consists of a series of exercises that will ensure you’ve got the basics on lock.

If you find there is a construct or challenge you’re unsure how to approach, seek guidance from the team. Asking questions is encouraged.

Setup

Fork the Lab Week 2 repo to your personal Github account and complete the exercises in that repo. (For design log purposes, this cloned repo will be the one you link to.)

The toolchain has already been setup for you for all the exercises. It uses techniques you have not been introduced to yet so don’t be concerned if you don’t understand all of it. You can build the simulations using the techniques from the Week 1 Onboarding Lab.

If you wish to test your work, you can do so by running the following command inside your build directory:

ctest --output-on-failure .

We’ll talk more about setting up and running tests in the next lab.

Exercise 1: Warm Up

Implement the following opcode table with a single combinational assign

statement.

| op | out |

|---|---|

| 0 | a + b |

| 1 | a - b |

| 2 | a & b |

| 3 | a | b |

Exercise 2: Sequential Logic

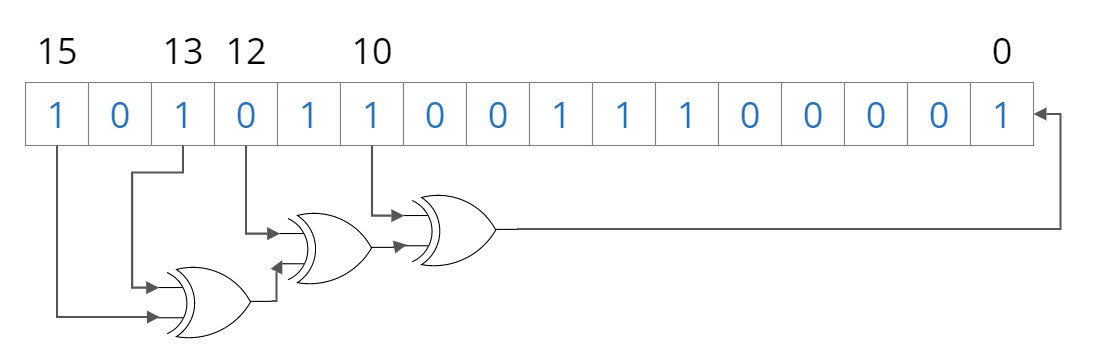

Implement an xor-based Fibonacci Linear Feedback Shift Register with taps at bits 15, 13, 12, and 10 (schematic provided below). If the reset is low, the LFSR should be initialized with the value present on the init input bus.

Step the output on positive clock edge.

Exercise 3: Module Composition

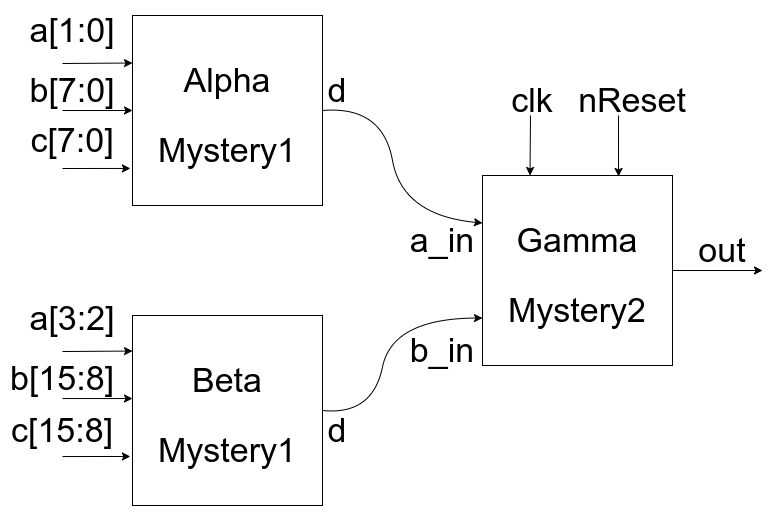

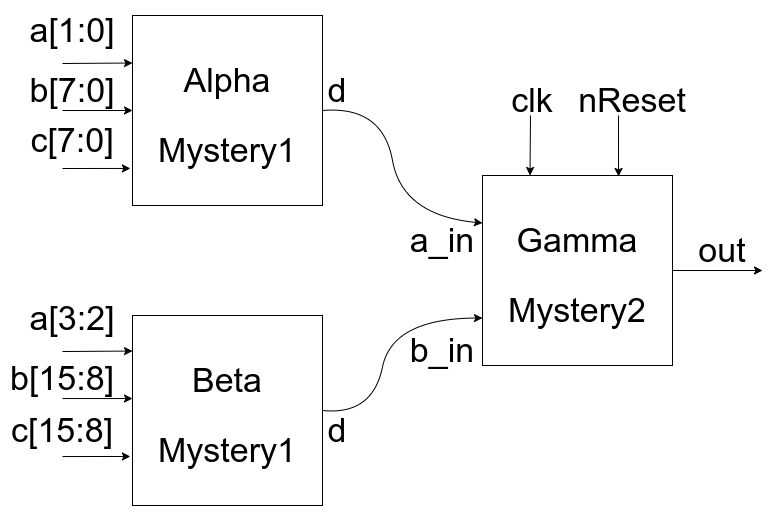

There are two Mystery modules under the Mysteries directory. Compose them according to the following schematic:

Make Note: In the next lab you’ll learn more about verification testing, but

for now take a quick glance at dv/exercise1.cpp, dv/exercise2.cpp, and

dv/exercise3.cpp. Exercise1 exhaustively tests all possible inputs,

Exercise2 samples some possible initial values for a hundred cycles, and

Exercise3 randomly tests inputs for a hundred cycles.

Why do you think the reason for these different testing approaches are? What are their advantages and disadvantages?

Exercise 4: Combinational Logic

Using an always_comb block, implement a decoder/mux that implements the

behavior described in the following table.

| cs | sel | out |

|---|---|---|

| 0 | X | 0 |

| 1 | 0 | alpha |

| 1 | 1 | beta |

| 1 | 2 | gamma |

| 1 | 3 | 0 |

Lab 3: Verification

Purpose

The layout of this lab is the same as the previous one, but the situation is reversed. Instead of having all the tests available and implemented already and filling in the SystemVerilog, the SystemVerilog is written and you will be implementing tests.

Testing, in the hardware world we call it “design verification”, is essential to ensuring that designs fulfill their intent. The options for repairing hardware that has already been fabricated are limited.

Background

In the Processor Design Team, design verification tests are regular C++

programs. If the program returns 0 from its main function, the test has

passed, if the program returns something non-zero, the test has failed.

The heart of a test is the model. The model is a simulation of the

device-under-test (DUT), synthesized from the SystemVerilog files which describe

it using a program known as verilator. You don’t need to worry about invoking

or using verilator directly, the toolchain does that for you.

The model is a C++ object, the public members of this object are the port list present on the SystemVerilog module. For example a module with the following port list:

module DUT(

input [7:0] alpha;

input [7:0] beta;

output [15:0] gamma;

);

Will generate a model with the following public members:

struct VDUT {

uint8_t alpha;

uint8_t beta;

uint16_t gamma;

};

When changing inputs, the outputs of the model can be evaluated using the

.eval() method. For example:

VDUT model;

model.alpha = 5;

model.beta = 8;

model.eval();

// model.gamma will change

Setup

Fork the Lab Week 3 repo

to your personal Github account and complete the exercises in that repo. (For

design log purposes, this cloned repo will be the one you link to.) Write your

C++ test bench code in the C++ source code files located in the dv folder

of the repo.

The toolchain has already been setup for you for all the exercises. It uses techniques you have not been introduced to yet so don’t be concerned if you don’t understand all of it. You can build the simulations using the techniques from the Week 1 Onboarding Lab.

Exercise 1: Something Familiar

Write a test that verifies the module implements the following behavior. Test

all possible values of a and b for each operation.

| op | out |

|---|---|

| 0 | a ^ b |

| 1 | a << b |

| 2 | a % b |

| 3 | ~(a & b) |

Exercise 2: Reading Rainbow

Being able to read code is as important as being able to write it. For this exercise, assume that the module is correct. This test is being written to ensure that any future changes to the module do not change its external behavior.

Design a test that reasonably verifies the behavior of the Exercise2 module. Note that testing the entire space of possible states is likely not viable.

Make Note: What testing strategy did you adopt for this Exercise2? What decisions did you have to make and how did you come up with your answers?

Exercise 3: A Verification in Many Parts

The Exercise3 module follows the same schematic as in Lab 2:

However, the mysteries have been changed. Mystery1 operates as follows:

- If

ais 0, thendis:

| Bits | 7:6 | 5:3 | 2:0 |

|---|---|---|---|

| Value | b’00 | b[2:0] | c[2:0] |

- If

ais 1, thendis:

| Bits | 7:6 | 5:3 | 2:0 |

|---|---|---|---|

| Value | b’01 | c[2:0] | b[2:0] |

-

If

ais 2, thendisb -

If

ais 3, thendisc

And Mystery2 operates according to the following rules:

-

Clocked on negative clock edge

-

When

resetis high, out is initialized to:

| Bits | 15:8 | 7:0 |

|---|---|---|

| Value | b_in | a_in |

- When

resetis low, the output cycles through the following states:

| State | Value |

|---|---|

| 0 | {a_in, out[7:0]} |

| 1 | {out[15:8], b_in} |

| 2 | {out[7:0], out[15:8]} |

| 3 | {out[3:0], out[7:4], out[11:8], out[15:12]} |

| 4 | {15’b0, ^out} |

Write a test that reasonably verifies the behavior of the module.

Exercise 4:

The Exercise4 module has the following behavior:

| cs | sel | out |

|---|---|---|

| 0 | X | 0 |

| 1 | 0 | alpha |

| 1 | 1 | beta |

| 1 | 2 | gamma |

| 1 | 3 | alpha & (beta | gamma) |

Write a test that reasonably verifies the behavior of the module.

Make Note: How does testing a Don’t Care work? What must be done to ensure the input truly has no effect on output?

Lab 4: Verification Toolchain

Purpose

This lab will be a walkthrough of the toolchain elements of verification. This will build on the toolchain lessons establish in Lab 1 and cover much of the material that was glossed over in Lab 3.

Some of the ideas that will be covered include: creating libraries of System Verilog modules, adding dependencies to a project, and using a testing framework.

Background

Oftentimes when building either software or hardware, we want to integrate

third-party components and libraries, code written by other people. To do this

we use a tool called a package manager. In the Process Design Team, the

package manager we use is called vcpkg. While vcpkg is

nominally a package manager for C/C++ projects, it’s suitable to be used with

any collection of files including with our SystemVerilog projects.

One of the dependencies we’ll be interested in for the purposes of verification will be a test framework. A test framework provides utilities for running and logging information about our design verification tests. Since correctness is very important to hardware development, these utilities will come in handy. The Process Design Team uses a test framework called catch2 for its design verification.

Setup

Fork the Lab Week 4 repo to your personal Github account. This repo features the same modules as Lab 3, but you will be converting your tests to use the catch2 framework. In addition, much of the toolchain code is not yet written. We will need to add it ourselves.

Registries

A registry is a collection of information about packages, where packages

are the source code files (SystemVerilog, C++, or even cmake files) that we wish

to use in our project. We keep track of the registries we’re using in a given

project with the vcpkg.json file.

If you look at the vcpkg.json file in the Lab 4 repo, you will

find something that looks like the following under "vcpkg-configuration":

{

"default-registry": {

"kind": "git",

"baseline": "6046e48163a26252f7a8f4aa036cbdd9eb793c20",

"repository": "https://github.com/microsoft/vcpkg.git"

},

"registries": []

}

This is a registry listing, a json object that tells vcpkg where to look for

packages. In this case, the only registry listed is the default-registry,

which is where vcpkg will search if a requested package is not listed for

any other registry. Here the default-registry is pointed at a git repo managed

by Microsoft, which has many useful packages in it. The registries list, which

would contain all other registries we wish to use, is empty.

We will need to add a registry to the registry list. The required fields for a registry are:

-

kind: What type of registry is this? For our purposes this will always be a git repository, so you can always put"git"here -

baseline: the git hash to pull from. We’ll cover where to get this in a moment -

repository: a link to the git repository -

packages: a list of packages you would like this registry to be responsible for

The Processor Design package registry is located at:

https://github.com/NYU-Processor-Design/nyu-registry

To add that registry to the registries list, the entry should look like this:

"registries": [

{

"kind": "git",

"baseline": "",

"repository": "https://github.com/NYU-Processor-Design/nyu-registry.git",

"packages": [

"nyu-*"

]

}

]

This is incomplete, we still need to add a baseline. In order to get the necessary hash, go the registry repo page and click on “commits”.

Then, on the commits page, click on the double square icon to copy the full hash to your clipboard. You can then paste this into the baseline field.

We briefly note that the packages field contains the string "nyu-*", this

tells vcpkg that this registry will provide every package that begins with

“nyu-”.

Dependencies

Now take a look at the rest of vcpkg.json, this file describes our project. It

should look something like this:

{

"name": "week-four-lab",

"version": "1.0.0",

"description": "Template for week four lab",

"homepage": "https://github.com/NYU-Processor-Design/onboarding-lab-4",

"maintainers": [

"Vito Gamberini <vito@gamberini.email>"

],

"license": "CC0-1.0",

"dependencies": [],

"vcpkg-configuration": {

...

}

}

The most important field to note is the dependencies list, it’s empty. Here is

where we’ll list the packages we need vcpkg to fetch for us.

The packages we’ll need for this lab are:

-

nyu-cmake: Utility functions forcmake. These functions make working with SystemVerilog more convenient -

catch2: The catch2 test framework mentioned above

Add these as a list of strings to the dependencies field of vcpkg.json. The

order you list them does not matter.

Libraries and Packages

Once a package has been listed as a dependency, vcpkg will fetch it for us

when we run cmake to generate our build files. We need to let cmake know

about these packages in order to be able to integrate them, and the command

to do this is called find_package().

The first package we’re going to need is nyu-cmake, so in the CML add the

following line of code after the project() command:

find_package(nyu-cmake CONFIG REQUIRED)

find_package() takes three arguments here:

-

nyu-cmake: this is the name of the package we wantcmaketo find -

CONFIG: this flag changes the search behaviorcmakeuses to find the package. If you’re curious to learn more, you can read about this in the official cmake documentation, but it’s not vital to understand -

REQUIRED: this flag tellscmaketo throw a build error if it cannot find the requested package

Next we need to create a library. This works just like creating an executable

from Lab 1, except the command is add_library() instead of add_executable().